# Miniball electronics for 2011

# Contents

| 1          | Foreword                                                                                | 3               |

|------------|-----------------------------------------------------------------------------------------|-----------------|

| 2          | Notation                                                                                | 5               |

| 3          | Overview                                                                                | 5               |

| 4          | The CD cabling                                                                          | 6               |

| 5          | The delayed CD quadrant signal                                                          | 6               |

| 6          | Generation of the gamma gate                                                            | 7               |

| 7          | Generation of triggers                                                                  | 7               |

| 8          | Generation of the DAQ dead signals                                                      | 8               |

| 9          | Generation of the DAQ trigger                                                           | 8               |

| 10         | Generation of the ADC gates and the TDC stops                                           | 9               |

| 11         | Generation of the EBIS window                                                           | 10              |

| <b>12</b>  | Generation of the off window 12.1 Multiple off-window mode                              | <b>10</b><br>12 |

| 13         | Generation of the on/off window                                                         | <b>12</b>       |

| 14         | The generation of the GFLT                                                              | <b>12</b>       |

| <b>15</b>  | The DGF BUSY/SYNCH loop                                                                 | <b>12</b>       |

| 16         | Changes for the Mesytech MADC32 modules                                                 | 13              |

| 17         | Note about special signals                                                              | <b>15</b>       |

| 18         | Generation of the T1 timestamp                                                          | <b>15</b>       |

| 19         | Generation of the proton supercycle timestamp                                           | 15              |

| 20         | Generation of the control signals for the scalers 20.1 Scalers in proton-triggered mode | 17<br>18        |

| <b>2</b> 1 | Generation of pattern unit control signal                                               | 18              |

| 22         | Generation of the forced readout                                                        | 18              |

| 23         | The pattern unit bits                                                                   | 19              |

| 24         | Laser on/off                                                                            | 19              |

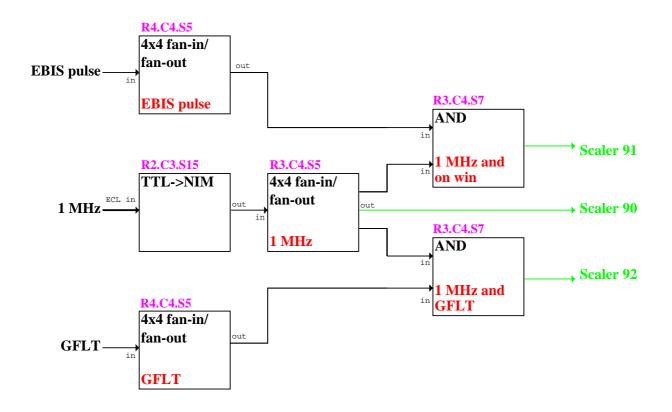

| <b>25</b>  | 1 MHz and EBIS, 1 MHz and GFLT                                                          | 20              |

| <b>26</b>  | The DAQ crash reset                                                                     | 20              |

| 27         | The Bragg chamber                                                                       | <b>2</b> 1      |

| 28         | The ionisation chamber                                                                  | 21              |

| 29         | DGF backplane bus                                                                       | 22              |

| 30         | Scalers                                                                                 | 22              |

$<sup>^1\</sup>mathrm{Nigel}$ Warr $14^{th}$  September 2011

| 31 | T-R          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>23</b>                                                                                                      |

|----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|    | 31.1         | Trigger generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23                                                                                                             |

|    |              | 31.2.1 ADC 0: 0x00F10000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24                                                                                                             |

|    |              | 31.2.3 ADC 2: 0x00F40000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26                                                                                                             |

|    | 91 9         | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $\frac{20}{27}$                                                                                                |

|    |              | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28                                                                                                             |

|    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                                                                             |

|    |              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                                                                                                             |

|    | 31.11        | Summary of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                                             |

| 00 | - CI         | , C. , . , . , . , . , . , . , . , . , .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.1                                                                                                            |

| 32 | Cna          | nges to g-factor experiments relative to T-REX setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31                                                                                                             |

| 33 | Posi         | tions of modules in crates and racks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>32</b>                                                                                                      |

| JJ |              | tions of modules in crates and racks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 04                                                                                                             |

|    | 77.1         | Rack 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 22                                                                                                             |

|    | 33.1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32<br>32                                                                                                       |

|    | 33.1         | 33.1.1 CAMAC crate R1.C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                                                                             |

|    | 33.1         | 33.1.1 CAMAC crate R1.C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32<br>33                                                                                                       |

|    | 33.1         | 33.1.1 CAMAC crate R1.C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32<br>33<br>34                                                                                                 |

|    |              | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32<br>33<br>34<br>34                                                                                           |

|    |              | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2                                                                                                                                                                                                                                                                                                                                                                                                                             | 32<br>33<br>34<br>34<br>35                                                                                     |

|    |              | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1                                                                                                                                                                                                                                                                                                                                                                                                     | 32<br>33<br>34<br>34<br>35<br>35                                                                               |

|    |              | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2                                                                                                                                                                                                                                                                                                                                                                             | 32<br>33<br>34<br>34<br>35<br>35<br>36                                                                         |

|    |              | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3                                                                                                                                                                                                                                                                                                                                | 32<br>33<br>34<br>34<br>35<br>35<br>36<br>36                                                                   |

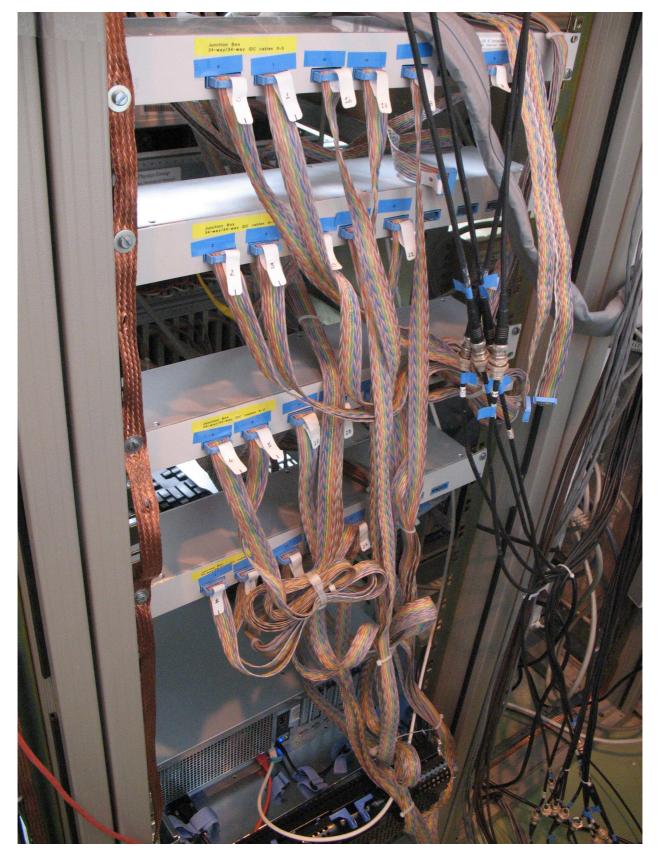

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies                                                                                                                                                                                                                                                                                        | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>36                                                                   |

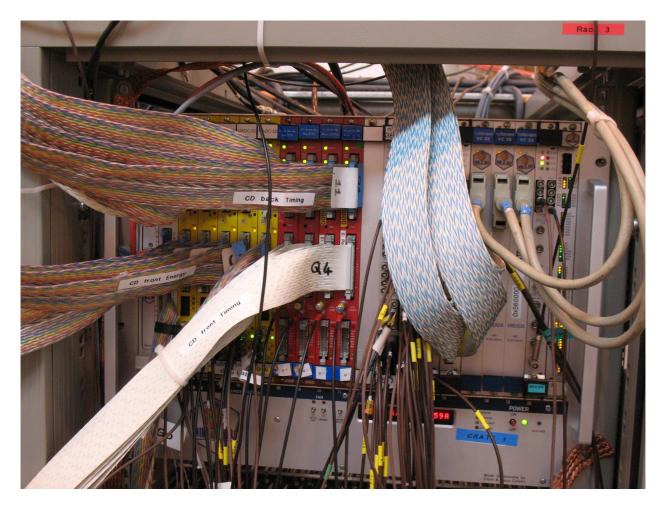

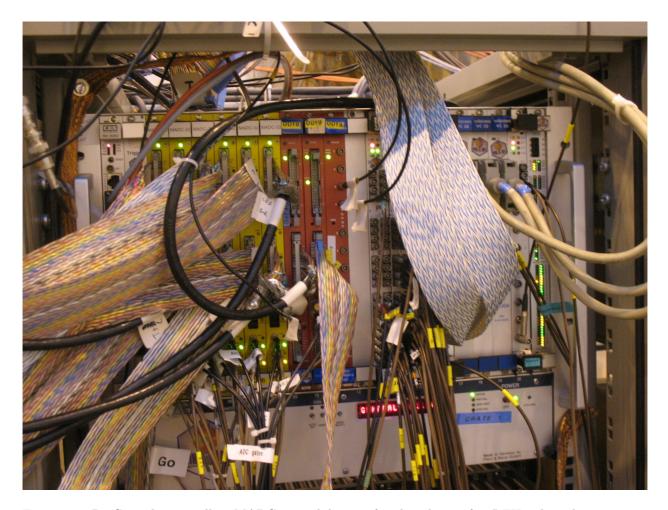

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3                                                                                                                                                                                                                                                                                 | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>36<br>37                                                             |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex                                                                                                                                                                                                                                               | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>36<br>37<br>37                                                       |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX                                                                                                                                                                                                              | 32<br>33<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>38                                                       |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2                                                                                                                                                                                       | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>36<br>37<br>37                                                       |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2                                                                                                                                                                                       | 32<br>33<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>38                                                       |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2 33.3.4 NIM crate R3.C3 33.3.5 NIM crate R3.C3                                                                                                                                         | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>37<br>37<br>38<br>39                                                 |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2 33.3.4 NIM crate R3.C3 33.3.5 NIM crate R3.C4                                                                                                                                         | 32<br>33<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>38<br>39<br>40                                           |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2 33.3.4 NIM crate R3.C3 33.3.5 NIM crate R3.C4 33.3.6 Preamp power - R3 rear Rack 4                                                                                                    | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>36<br>37<br>37<br>38<br>39<br>40<br>42                               |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2 33.3.4 NIM crate R3.C3 33.3.5 NIM crate R3.C4 33.3.6 Preamp power - R3 rear                                                                                                           | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>36<br>37<br>37<br>38<br>39<br>40<br>42<br>43                         |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2 33.3.4 NIM crate R3.C3 33.3.5 NIM crate R3.C4 33.3.6 Preamp power - R3 rear Rack 4 33.4.1 CAMAC crate R4.C1                                                                           | 32<br>33<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>38<br>39<br>40<br>42<br>43<br>43                         |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2 33.3.4 NIM crate R3.C3 33.3.5 NIM crate R3.C4 33.3.6 Preamp power - R3 rear Rack 4 33.4.1 CAMAC crate R4.C1 33.4.2 CAMAC crate R4.C2                                                  | 32<br>33<br>34<br>35<br>35<br>36<br>36<br>37<br>37<br>38<br>39<br>40<br>42<br>43<br>43<br>44                   |

|    | 33.2         | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2 33.3.4 NIM crate R3.C3 33.3.5 NIM crate R3.C4 33.3.6 Preamp power - R3 rear Rack 4 33.4.1 CAMAC crate R4.C1 33.4.2 CAMAC crate R4.C2 33.4.3 R4.C3                                     | 32<br>33<br>34<br>35<br>35<br>36<br>36<br>36<br>37<br>37<br>38<br>39<br>40<br>42<br>43<br>44<br>45             |

|    | 33.2<br>33.3 | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2 33.3.4 NIM crate R3.C2 33.3.5 NIM crate R3.C4 33.3.6 Preamp power - R3 rear Rack 4 33.4.1 CAMAC crate R4.C1 33.4.2 CAMAC crate R4.C2 33.4.3 R4.C3 33.4.3 R4.C3 33.4.4 NIM crate R4.C4 | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>37<br>37<br>38<br>39<br>40<br>42<br>43<br>44<br>45<br>46             |

|    | 33.2<br>33.3 | 33.1.1 CAMAC crate R1.C2 33.1.2 NIM crate R1.C3 33.1.3 NIM crate R1.C4 33.1.4 NIM crate R1.C5 Rack 2 33.2.1 KM-6 crate R2.C1 33.2.2 KM-6 crate R2.C2 33.2.3 New DAQ computer and raid array R2.C3 33.2.4 CD connectors and power supplies Rack 3 33.3.1 VME crate R3.C1 for Coulex 33.3.2 VME crate R3.C1 for T-REX 33.3.3 NIM crate R3.C2 33.3.4 NIM crate R3.C2 33.3.5 NIM crate R3.C4 33.3.6 Preamp power - R3 rear Rack 4 33.4.1 CAMAC crate R4.C1 33.4.2 CAMAC crate R4.C2 33.4.3 R4.C3 33.4.4 NIM crate R4.C4 Rack 5       | 32<br>33<br>34<br>34<br>35<br>36<br>36<br>37<br>37<br>38<br>39<br>40<br>42<br>43<br>43<br>44<br>45<br>46<br>47 |

#### 1 Foreword

This document describes the state of the electronics used at CERN for the May 2011 setup. Each iteration of this documentation is based on the previous year's back to 2004.

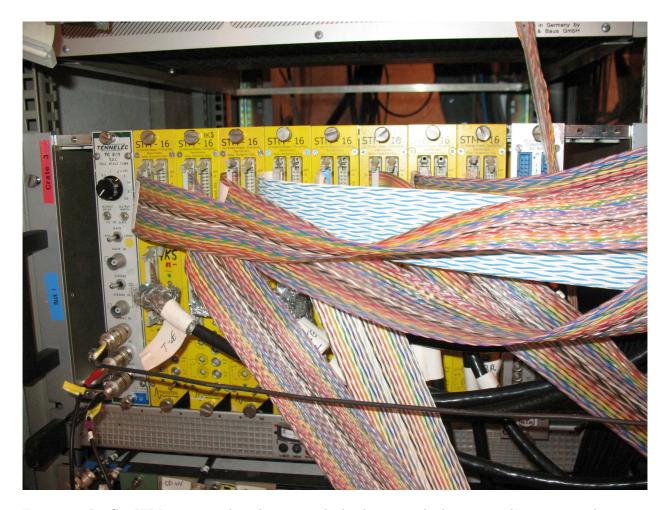

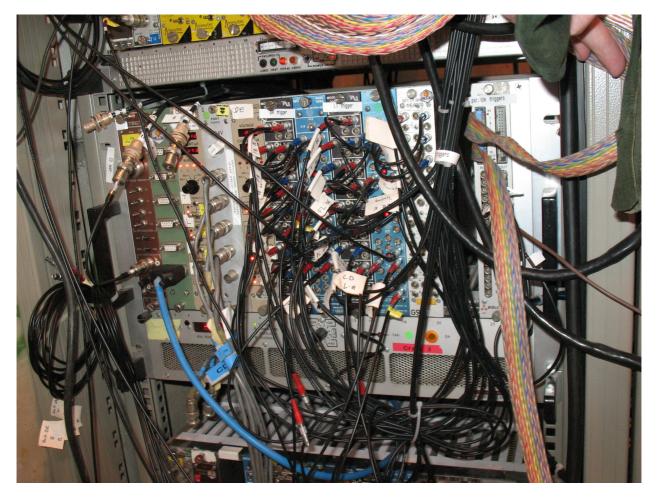

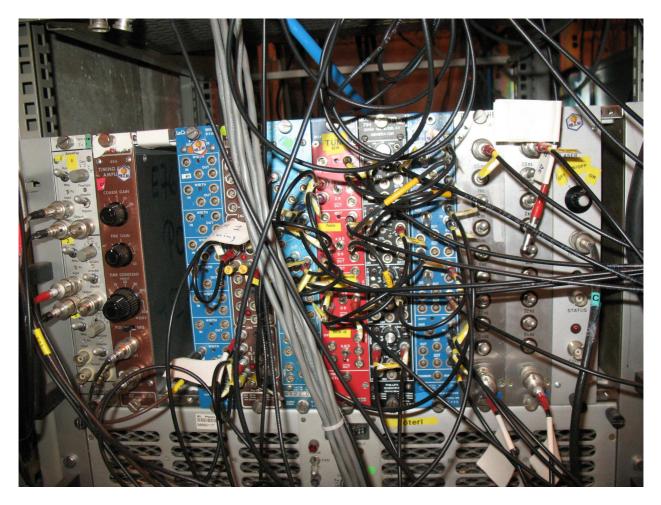

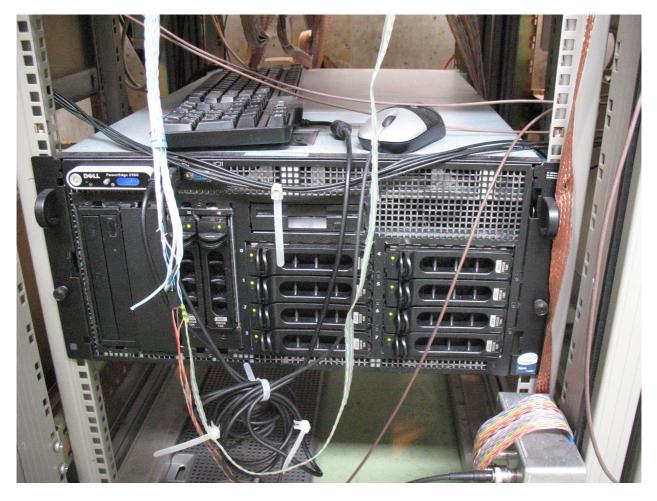

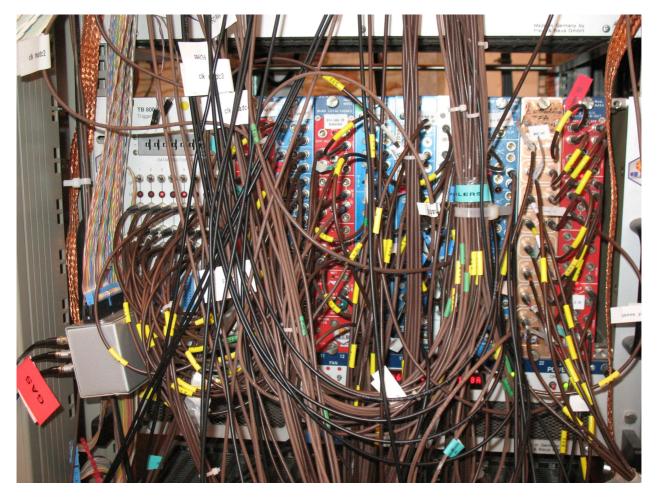

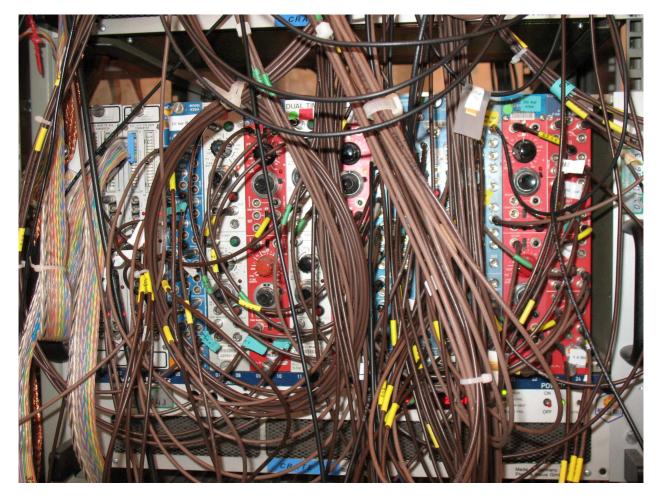

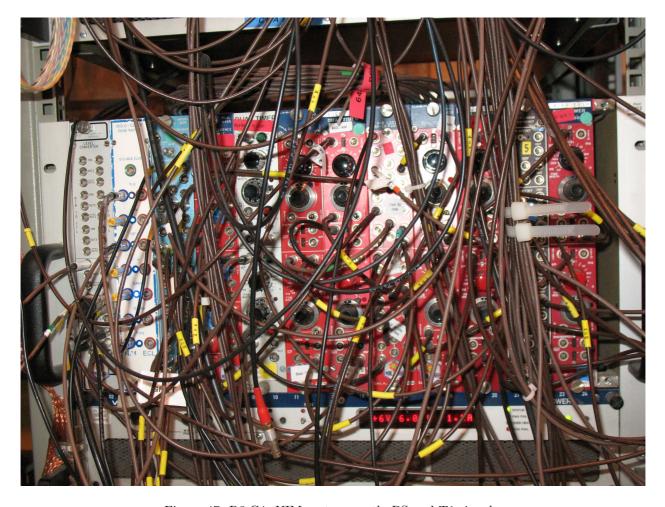

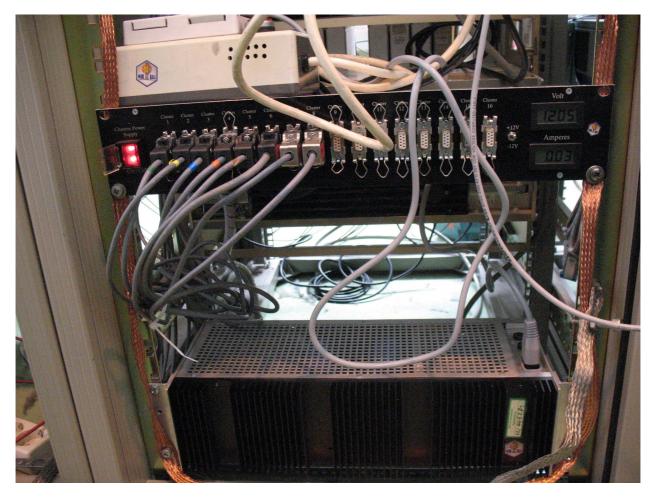

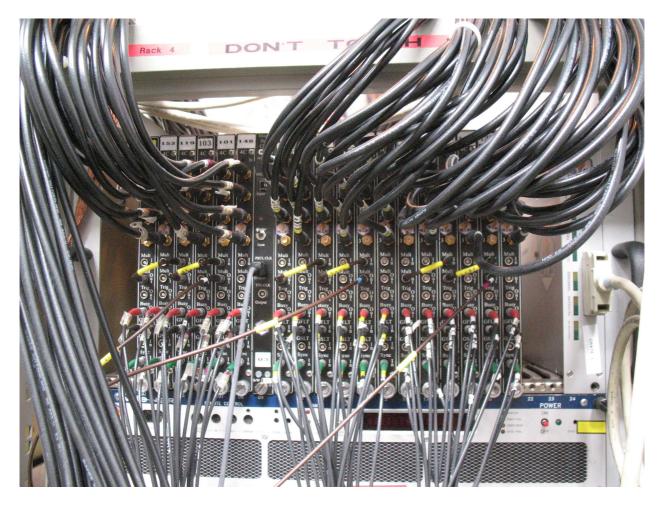

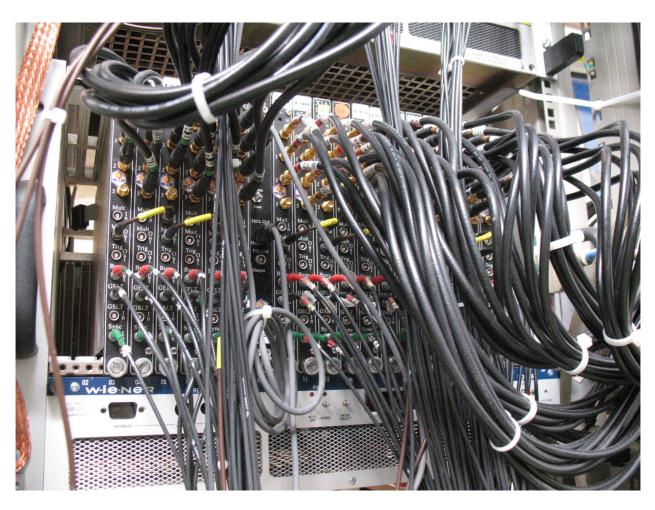

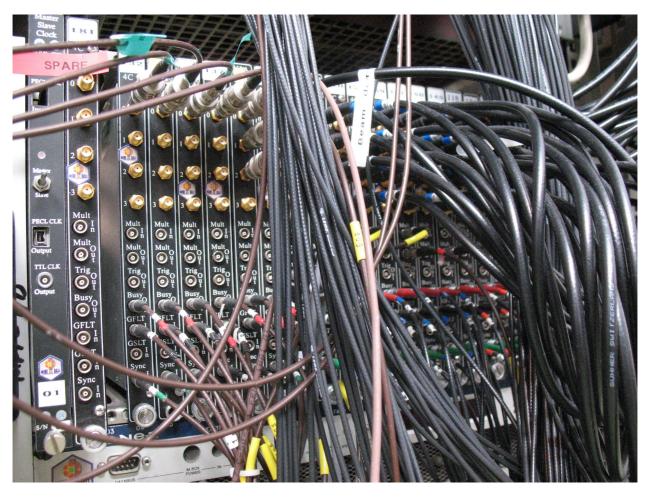

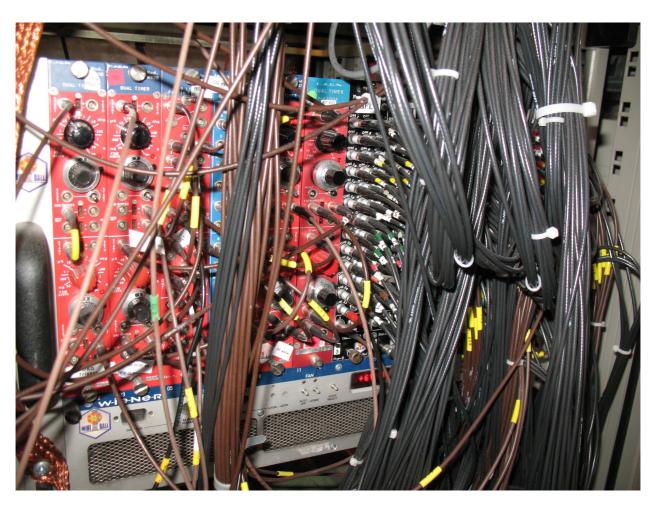

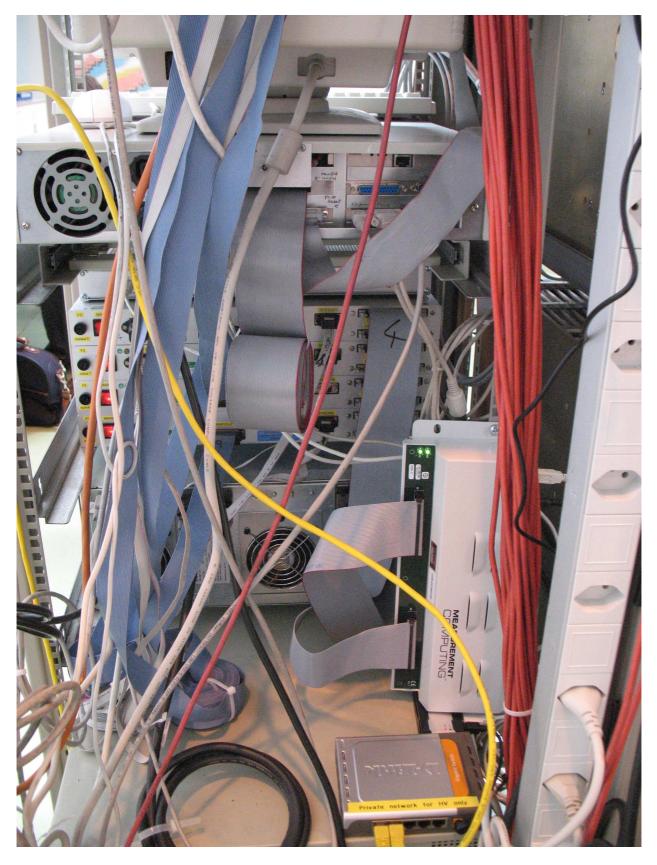

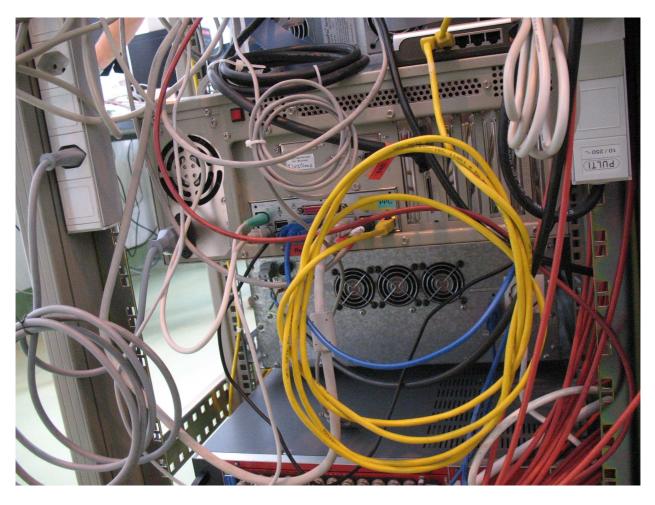

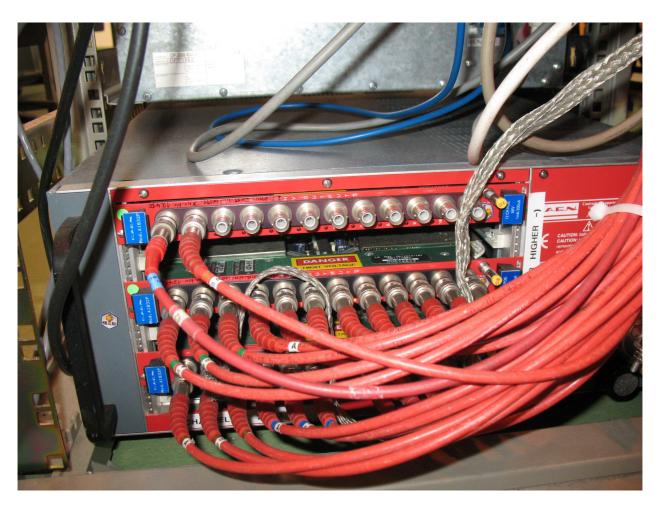

Figure 1: The Miniball electronics in 2011.

The differences to 2004 to 2005 have been indicated, notably the addition of laser on/off bits in the pattern unit and the Munich ionisation chamber, and changes in the TDC cabling. That means it is different to all previous experiments and is likely to be different to future ones. However, there should be certain similarities.

The electronics for this setup has grown gradually rather than being thought out as a single setup, so modules were not necessarily placed in the optimal position in the crates. In places, signals were duplicated due to different people building different parts of the setup and not realizing that the signal they were constructing was already available elsewhere.

In November 2004, a part of the electronics was dismounted and sent to GSI, Darmstadt, and the racks were all moved in order to allow for the building work to extend the ISOLDE hall. However, care was taken then to label things, so that they could be put back together. In May 2005, we put the things back together and it is believed that the state of November 2004 was achieved. In doing so, we noticed some changes with respect to the July 2004 setup. These all seem to be deliberate improvements.

However, the setup works, so there is no reason to change it for this campaign, but it could be improved on in the future.

Caveat: this document was produced during the setup with all the interruptions that that entails, so it probably contains mistakes. Several mistakes have already been found and corrected. There are likely to be others! Also people were still modifying the electronics while I was noting down the configuration. Use it with caution!

The main difference between the 2003 and 2004 setups is that in 2003 all of the CD was treated as one unit, whereas in 2004, each quadrant was dealt with separately. Also, in 2004 we took the ADC busy directly from the ADC module, whereas in 2003 we generated our own signal which was longer than the one generated by the module. Back then, we thought (erroneously) that the ADC was giving a busy signal which was too short and was the reason for mismatches in the number of ADC gates and the number of timestamper DGF events. In fact, the problem turned out to be due to the DGF sometimes missing the last event, so there was no reason to artificially generate the ADC busy.

Part way through 2005, a change was made to the way the TDCs were triggered. Before this change, a signal was generated from the particles and sent via an NIM to ECL converter to one of the last 16 channels of the TDC. After the modification, flat cables were taken from the MALUs giving the hit pattern in the front part of the CD, combined together in pairs (i.e. 8 signals from 16 rings). However, they weren't cabled very logically, so that for the ADCs had the front part of the CD on channels 0 to 15 and the back on 16 to 27 with 27 to 31 unused, but the TDCs had the back of the CD on channels 0 to 11, 12 to 15 unused and the front on 16 to 23. For 2006, we have adopted the same convention for the TDCs as for the ADCs, so the front is first and the back comes after. Consequently, we removed the NIM to ECL converter that was used for this.

In 2005, we also used the Miniball HV main frame to produce the high voltage for the beam dump detector. Prior to that we used a NIM power supply.

Another minor change in 2006: we moved the TDCs one slot to the left and put the ADC for the ionisation chamber to their right, rather than having the ionisation chamber ADC between the ADCs and TDCs for the CD. We also swapped a VME scaler with NIM inputs and the adjacent VME scaler for the PPAC.

In 2007, all the electronics was moved from the platform down to the new hall. However, very little was changed during this move. The main differences are in the electronics to the Bragg chamber. Also, the  $\Delta E$  detectors, which have not been used in the last few campaigns, but had been cabled in the electronics racks, were not put in the electronics this time.

At the end of 2007, an extra crate was put into rack 1, which was empty at the start of the 2008 campaign. This has the result of renumbering the bottom crate in that rack. Also an ECL  $\rightarrow$  NIM converter in that crate was moved from the first slot to the last, as some additional cables were added for the Munich setup, which were too short otherwise.

The last scaler (Bragg chamber) was modified in 2008. In 2007 it was added as an afterthought and it was not documented. It used a linear amplifier on the analogue signal going to the VME sampling ADC and sent this signal directly into the scaler. The additional amplification made it go above the threshold of the scaler, so it counted. However, this is an ugly way of doing things! In 2008, the logical output of the sampling ADC was used. However, as this signal is needed for the logic, it is only accessible after gating with the GFLT and the DAQ not dead signals. This shouldn't matter, as we don't expect particles in the Bragg chamber when there is no beam and we can't count them if the DAQ is dead.

The biggest change in 2008 is to the autofill system. This is especially complicated as it was desired to have both the old and the new systems available. The old system runs on pcepsc22 and the new on the old DAQ computer pcepuis20. The old system uses ISA cards inside the DAQ computer with two flat cables which connect to manifolds B and D (a small flat cable connects A with B and C with D). The new system uses an external USB unit with two flat cables, which are pin-to-pin compatible with the old system and likewise go to manifolds B and D. The old system uses a custom-made PT100 box which is connected to the PC with a flat cable. The new system uses a different PT100 box, which is connected by two USB cables.

In May 2009 the CAEN V785 VME ADCs were replaced with Mesytech MADC32 modules. These modules are capable of timestamping the data with a 40 MHz clock like the DGFs, so it should be possible in future to do away with the timestamper DGFs. However, for the 2009 campaign, we retain both possibilities. i.e. the gate sent to the Mesytech ADCs is sent to the signal input of a DGF to generate a timestamp. This should be approximately the same as the timestamp from the Mesytech's own clock. So this data is duplicated in the list mode. If the Mesytech data proves reliable, we can in future campaigns leave out the timestamper DGFs. Note, however, that the timestamper DGFs for the EBIS, T1 and PS signals have to remain. For convenience and to allow a fast switch back to the CAEN modules if the Mesytech modules don't work, the same VME addresses have been used for both, so it is just a matter of switching the modules and taking the Marabou configuration from 2008.

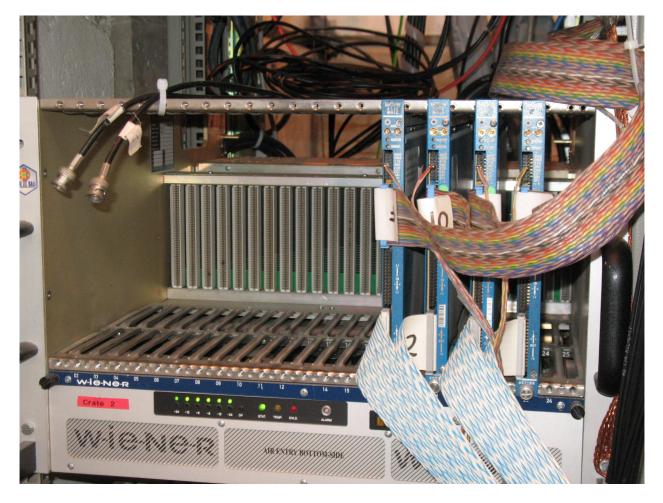

The differences from 2009 to 2010 are mainly because the T-REX setup was installed in the autumn and I have tried to set up the Coulex setup without dismantling too much of the T-REX setup. As a result, there is an extra crate in rack 4 and the modules are in different places in those crates. Also, we inadvertently shifted all the ADCs and TDCs one slot to the left in the VME crate R3.C1.

There are no big changes from 2010 to 2011. The CD pulser is in a different place and the order of the modules in the VME crate has changed, so the ionisation chamber MADC is next to the other MADCs. This makes switching to T-REX easier, because T-REX just replaces the four TDCs with an MADC, a QDC and two ADCs. The VME addresses of the modules are as in 2010.

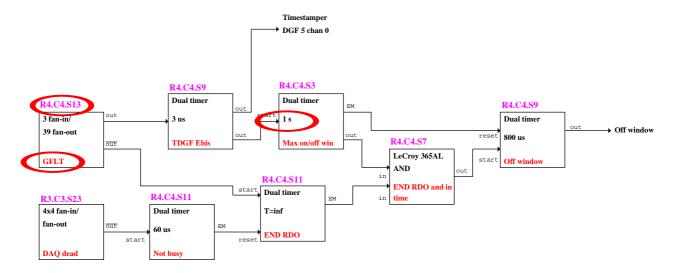

A new feature was added in June 2011 to try to prevent file corruption we were observing at high EBIS rates (actually the fake 100 Hz EBIS rate we use for acquiring with sources). Two extra wires were added from DAQ dead (not from DAQ dead +) in R3.C3.S23 to the vetoes of the gate generators "EBIS pulse" (R4.C4.S3) and "off window" (R4.C4.S9). This suppresses the GFLT (which is the OR of these two signals) whenever the DAQ is dead. It seems to prevent file corruption even at 1000 Hz fake EBIS rate. However, I still do not understand why this is needed. The Busy/Synch loop of the DGFs should take care of this.

In July 2011, Fredrik managed to improve the slow extraction so that the EBIS pulse lasted a bit over 900  $\mu$ s, so we changed the on and off window lengths from 800  $\mu$ s to 1 ms.

### 2 Notation

I have used the notation "R2.C4.S13" to mean rack two (starting at 1 nearest the wall) crate four (starting with 1 at the top), slot 13. Similarly "R2.C4" means all of crate four of rack two. In the diagrams, the location of the modules is indicated in magenta.

#### 3 Overview

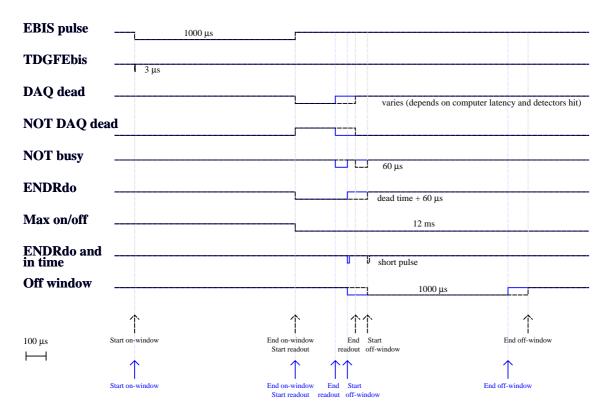

Miniball acquires during two time windows, referred to as the "on window" and the "off window". The "on window" is generated when the EBIS sends a signal to indicate it is about to send beam to us. The window was 800  $\mu$ s wide, as even in slow extraction mode, this is larger than the real beam pulse, even allowing for the delay between the EBIS pulse and the beam arriving at Miniball. However, in 2011, it seems that the slow extraction is now better and the window had to be extended to 1 ms. After the "on window" we read out all the data. Normally, there is then sufficient time to take data again off beam and read that out, before the next beam pulse. We refer to this as the "off window" and it should have the same length as the "on window". The "off window" should, therefore, be pure background. So we can subtract one from the other to get the contribution from the beam. Note that the "on window" is sometimes referred to as "EBIS" because it is generated by the EBIS.

The logical OR of the "on window" and "off window" is used to validate the gamma data using the GFLT (global first level trigger) input of the Xia DGFs used to acquire this data. So the term "GFLT" is equivalent to the OR of these two windows. The DGFs acquire any gammas that arrive within either window. The DGFs record the energy and a timestamp with 25 ns ticks. The logic for this is mostly in the left part of R4.C4.

The particles are acquired using Mesytec MADCs for the energy and Caen V775 TDCs for the time. The MADCs, like the DGFs, record an energy and a timestamp with 25 ns ticks. The same 40 MHz clock is used to generate both timestamps and they are synchronized. Additional DGFs are used to record timestamps for the EBIS, T1 (impact of proton on primary target) and PS (start of supercycle of PS-Booster).

The gate for the MADCs and the common stop for the TDCs is generated for each quadrant of the CD independently. It is the logical OR of "downscaled particle" and "particle-gamma coincidence". That is, we have a gate every time, there is a particle-gamma coincidence, but we might downscale pure particle events if the rate is high. The multiplicity output of the DGFs is used to generate the gamma signal, which is used to make the particle-gamma coincidence.

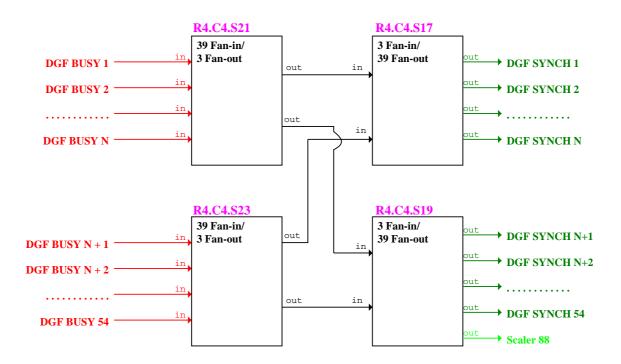

The right part of R4.C4 is used for the GFLT and also the BUSY-SYNCH loop, which is used to synchronize the timing of the DGFs and MADCs. Each DGF generates a BUSY output when it is not able to accept data (e.g. it is being read out or is stopped) and these are ORed together to make the SYNCH signal. This is sent back to all the modules. The SYNCH is equivalent to "one or more DGFs are busy".

The signals from the CD go to RAL109 amplifiers in R2.C1 (front annular strips) or R2.C2 (back sector strips). These produce an energy signal which goes directly to the MADCs in R3.C1 and an ECL logic signal. The logic signals for the back timing go to the TDCs in R3.C1, while the ones for the front timing go to MALUs in R1.C2 to be ORed together to make the particle triggers (one per quadrant). They are, however, also sent to the TDCs in R3.C1.

We need to veto events if some part of the system is busy, so we have "DAQ dead" meaning that the trigger module in the VME crate R3.C1 is asserting that the DAQ is busy (either due to a readout or due to a stopped acquisition). We have "SYNCH" which indicates that one or more DGFs are busy. We also have an "ADC busy" for each quadrant of the CD, indicating that the corresponding MADC is busy (i.e. being read out or in a stopped state).

The logic for handling the T1 and PS signals which come via a patch panel from the ISOLDE control room, is a bit complicated because they might come while the DAQ is being read out. Most of this logic is in R3.C4 with some in R4.C4.

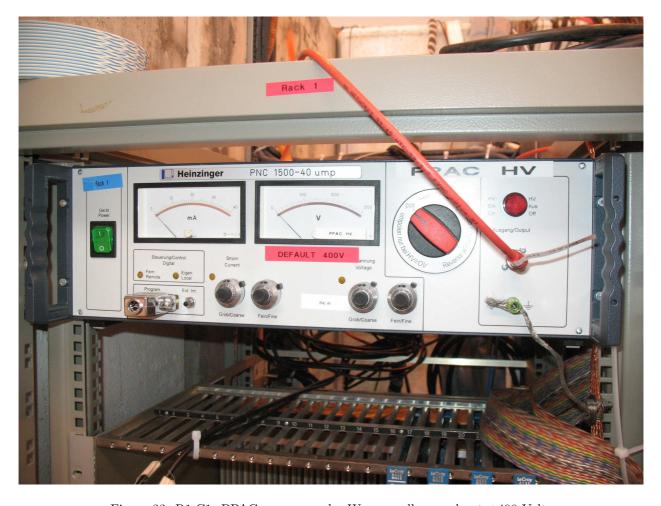

Rack 1 contains various odds and ends. R1.C4 has the preamp power for the beam dump detector, the CD pulser and the CD high voltage. R1.C5 has modules for the ionisation chamber.

### 4 The CD cabling

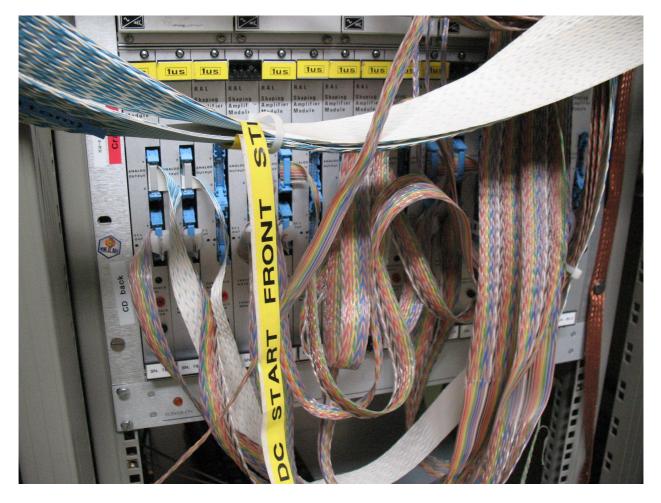

There are two crates of RAL109 shaping amplifier modules. The top one (R2.C1) is for the 16 front rings and the bottom one (R2.C2) is for the 24 back sectors.

The analogue outputs of the RAL109s for the front go directly to channels 0 to 15 of the Mesytech MADC32 VME ADCs in R3.C1.3-6 (i.e. the lower part of the ADCs).

The analogue outputs of the RAL109s for the back also go directly to channels 16-31 of the same ADCs, but since we only use 12 signals (we combine the 24 sectors per quadrant of the back of the CD into 12 signals, by connecting them pairwise - this is done in the hardware) there are some channels spare. By picking off a couple of the wires from these cables, the CD PAD detector (another RAL109 in R2.C1) and the laser power (from the laser control box) are also put into the ADCs.

The ECL outputs of the RAL109s for the front are connected into the four MALU modules (R1.C2.S17,19,21, 23). From there, the ORO signals are connected via a flat cable, where the ends have been split at the MALU end, to an ECL to NIM converter (R1.C4.S23). Also, flat cables connect the outputs of the MALUs to the CAEN V775 32-channel TDCs in R3.C1.7-10 (channels 0 to 15, i.e. the lower part).

For the back sectors, the ECL outputs are connected directly to the same TDCs on channels 16-31 (i.e. the upper part).

Additionally channels 0 and 1 of the laser box are connected to channels 28 and 29 of the quadrant 1 ADC (R3.C1.S3). It looks like the latter one is the laser power.

The signals from the PAD detector come from a different RAL109 in R2.C1 and should each be connected to channel 30 of the ADCs (R3.C1.S3-6). This is done by splitting off two channels from the flat cable and connecting them individually. However, because of the modification to the cable for quadrant 1 in order to add in the laser power (actually, a new cable was made - it is blue and white, while the others are multicoloured), it looks as though quadrant 1 of the PAD detector isn't connected any more.

Probably, we should make a new cable for quadrant 1, with both the PAD and the laser power.

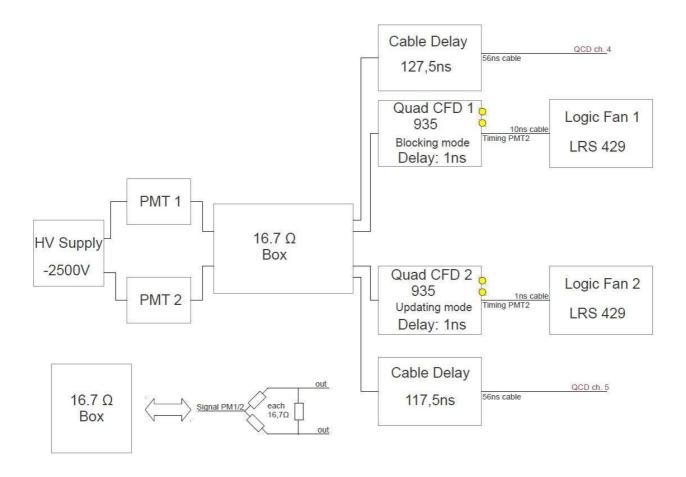

### 5 The delayed CD quadrant signal

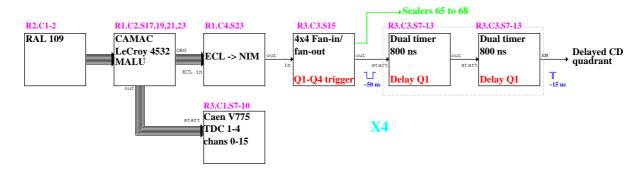

Figure 2: The generation of the delayed CD quadrant signal. This is done for each of the four quadrants of the CD.

From the CD we need to generate logic signals to indicate when an event has occurred in a given quadrant. Note that in previous setups we treated the whole CD as one, but now we treat it as four independent quadrants.

For each quadrant, we take the logic output from the RAL 109 shaper amplifiers via a flat cable to four CAMAC MALU units. Note that although these are CAMAC modules, we do not need to program them, so they are in a crate without a CAMAC crate controller. They just take their power from the CAMAC crate.

Each MALU gives a differential ECL ORO output (this is just an OR of all the inputs) and these signals for all four MALUs are combined on a single flat cable and sent to an ECL  $\rightarrow$  NIM converter. From there, the signal for each quadrant goes into one quarter of a 4x4 fan-in/fan-out module and then is used to start a dual timer.

We use two copies of the signal from this fan-out.

- One goes to a scaler. We use scaler 65 for quadrant 1, scaler 66 for quadrant 2 etc.

- One copy is delayed by 800 ns to generate the delayed CD quadrant signal.

We want to delay this signal by 800 ns, but the CAEN dual timers have the property that if a second signal arrives during that time, the end marker comes 800 ns after the **second** signal, not the first. So we use half of a dual timer to generate a signal which is 800 ns wide and then use that to start the second half of the same module also set to 800 ns (so both start more or less simultaneously, but the delaying of the end

marker is suppressed). We then take the end marker from the second half of the module. There are probably better ways to do this. In all probability this behaviour of the dual gate is a feature but it doesn't seem to be possible to turn it off and the manual is utterly useless. Perhaps a different kind of gate generator would be better, or a discriminator followed by a gate generator. In future years we should really rethink this part.

For all four quadrants, we use four MALUs, one ECL  $\rightarrow$  NIM converter, one fan-in/fan-out module and four dual timers.

Note that the RAL109s and the NIM crate containing the NIM  $\rightarrow$  ECL converter are in the CD electronics rack, and the CAMAC crate with the MALUs are in the leftmost rack.

Previously, we took a third copy of the signal from the fan-out, passed it through a NIM to ECL converter and used it to start a TDC channel for each quadrant. Some time in 2005 this was changed and now, we take an additional flat cable from each MALU to the corresponding TDC so we have a hit pattern rather than just the OR.

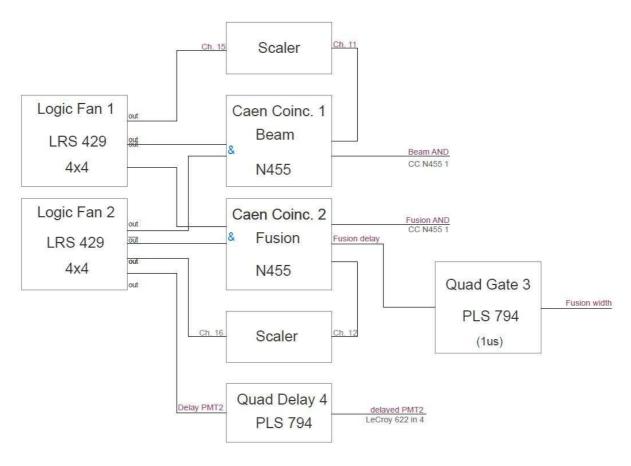

### 6 Generation of the gamma gate

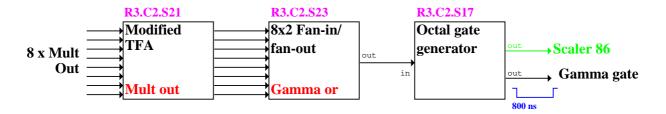

Figure 3: The generation of the gamma gate. This is the logical OR of all the signals from the Ge cores.

We need to generate a signal indicating that one of the Ge detectors has an event. To do this we take the Mult Out (35 mVolt per hit) from the DGF having the first core signal and put it into the Mult In of the next DGF with a core signal (i.e. the third DGF) and from its Mult Out to the DGF with the third core. We then send this signal (i.e. one for each of the eight clusters) to a specially modified TFA (which contains eight Ge preamplifiers set to saturate with a 35 millivolt signal and generate a -0.8 Volt NIM output). In other words, the special module simply converts the 35 mV per hit signal into NIM logic. This signal is passed into a fan-in/fan-out.

This signal is used to generate the particle-gamma coincidence. Note that its width is determined by the DGF parameter FTPWIDTH.

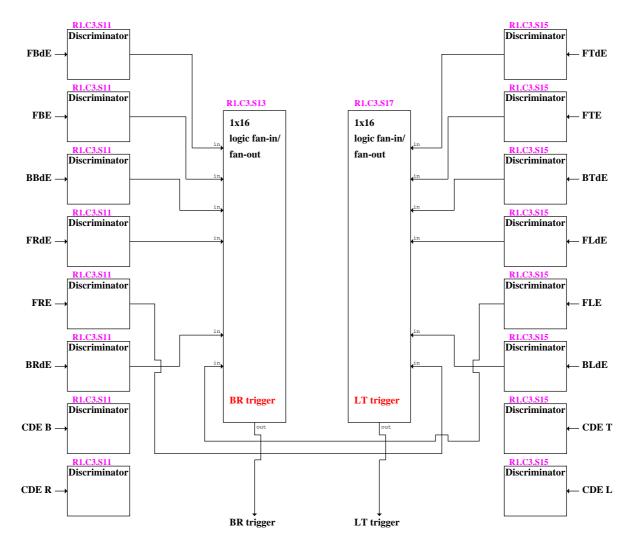

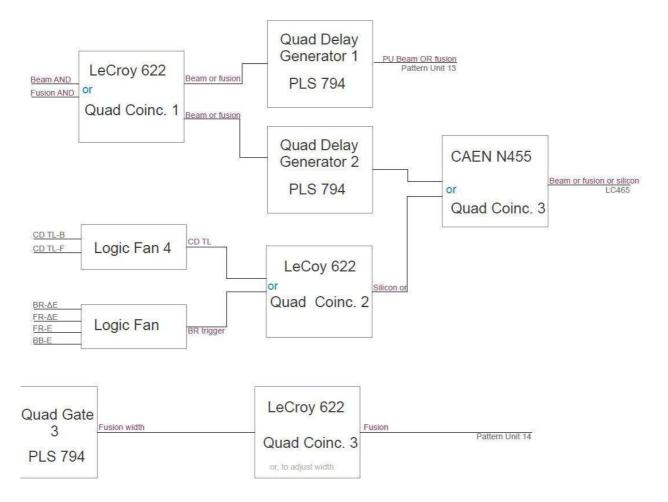

# 7 Generation of triggers

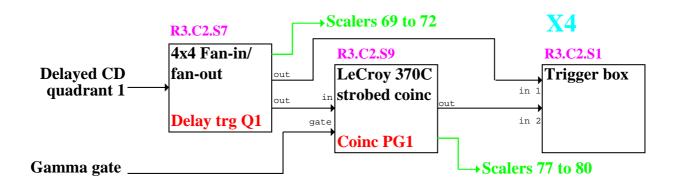

Figure 4: The generation of the triggers. The gamma gate is common to all four quadrants of the CD, but the rest is repeated for each quadrant with the second quadrant using channels 3 and 4 of the trigger box, the third using 5 and 6 and the last quadrant using the two remaining channels 7 and 8.

The delayed CD quadrant signal for each quadrant is passed to a fan-in/fan-out unit (a different quarter of the unit for each quadrant) and for each quadrant, we use three copies of this signal.

- One goes directly to the trigger box where it is downscaled (downscaled particles).

- The second goes into a strobed coinc unit and from there to the trigger box. The strobed coinc unit gates each input (one for each quadrant of the CD) with the gamma gate (see section 6). This gives the particle- $\gamma$  coincidence.

• The third copy goes to a scaler.

Scaler 69 has the delayed trigger for quadrant 1 and scaler 77 has the particle- $\gamma$  coincidence for that quadrant. Scalers 70 and 78 have the corresponding signals for the second quadrant etc.

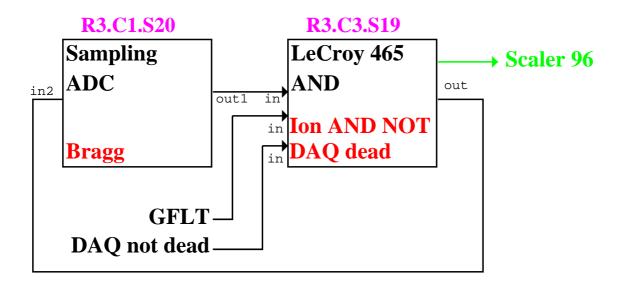

### 8 Generation of the DAQ dead signals

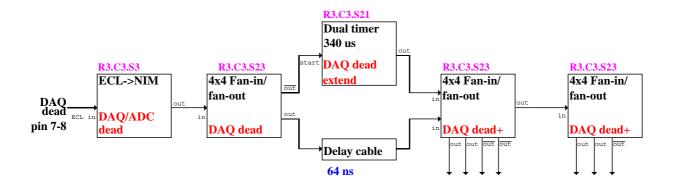

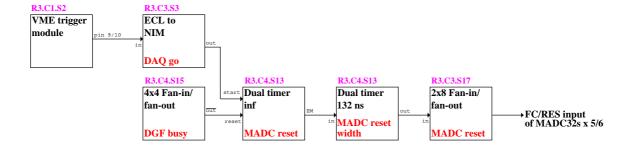

Figure 5: The generation DAQ dead signals.

The VME trigger module has an ECL output indicating that the DAQ is dead on pins 7-8 (note that pins 1-2 are the lower ones and 15-16 the upper ones). This goes through an ECL to NIM converter, after which it is split into two. One part is delayed by a 64 ns cable and the other part is used to start a gate at the end of the DAQ dead time. The idea is to extend the DAQ dead produced by the VME trigger by a fixed amount. If we were to do this without the delay, we might get a short glitch where it goes not dead between the end of the output from the VME trigger module and the beginning of the extension. After that it is fanned out.

In 2007, the DAQ dead extend was 340  $\mu$ s.

This bit was changed quite a lot between July and November 2004. We use seven DAQ dead signals, three of which are inverted. These come from the top two halves of the fan-in/fan-out in R3.C3.S23. The four normal outputs are used to veto the LeCroy 465 AND modules in R3.C2.S13 and R3.C2.S15 (one for each quadrant of the CD - note that the ANDs are triple modules, so the three quadrants are on one module and the fourth on the other). The three inverted outputs are used to generate the "not busy" signal (R4.C4.S11), the "DAQ trig if DAQ not busy" (R3.C2.S15) and the "Ion and not DAQ dead" (R3.C3.S19).

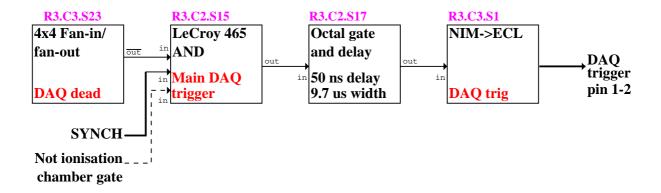

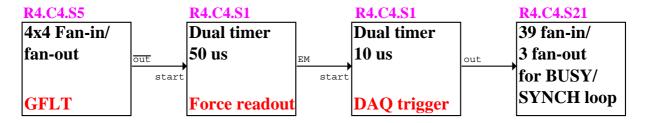

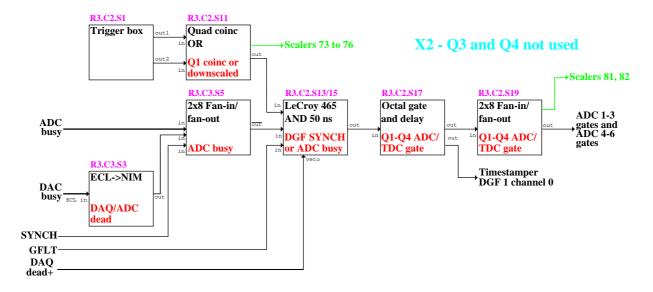

# 9 Generation of the DAQ trigger

Figure 6: The generation DAQ trigger. The ionisation chamber part is shown dashed because it was not present for all experiments.

We use the DGF SYNCH to trigger readout (having ensured that we force a SYNCH at the end of the on/off window etc. - see section 22) However, if we send a DAQ trigger while the DAQ is busy, the trigger module ignores it, so we need to postpone the DAQ trigger until the DAQ is no longer busy, otherwise it hangs. Since the SYNCH remains set until readout occurs, we AND this signal with the inverted DAQ dead signal, so that the moment we have both SYNCH and the DAQ is live, we generate a DAQ trigger.

The NIM  $\rightarrow$  ECL converter module is the same one used for the ADC busy lines and we have a special flat cable which connects the four ADC busy lines and the DAQ dead output from the VME trigger module to different channels of this unit. We use the first trigger (pins 1-2, which are the lower ones of the ECL input on the VME trigger module).

It seems that between July and November 2004, this bit was changed a little, presumably to prevent deadlocks in the DAQ.

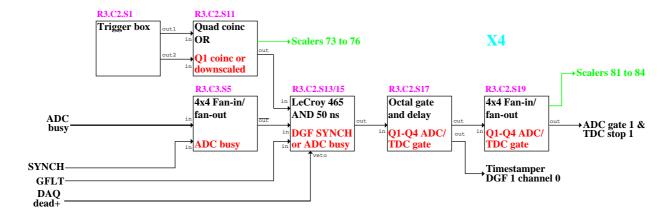

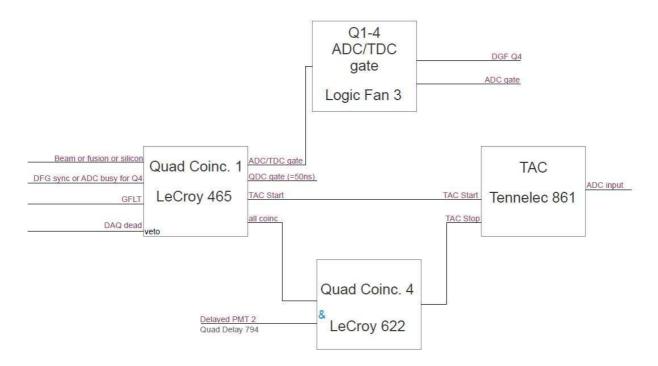

## 10 Generation of the ADC gates and the TDC stops

Figure 7: The generation of the ADC gates and TDC stops. Note that we have separate gates for each quadrant of the CD. This diagram shows the connections for the first quadrant. For the second quadrant we use channels 3 and 4 of the trigger box and so on. Note that for the MADC32, the busy signal is NIM, so the ECL to NIM converter is not needed.

In 2003 the ADC gate and TDC stop was the same for all parts of the CD, but in 2004 we changed it to have separate gates for each quadrant.

We want to generate an ADC gate, a TDC stop and a signal for the timestamper DGF corresponding to a given quadrant (four separate gates, four separate stops and four timestamping DGFs) all of the following conditions are satisfied:

- The trigger box gave a signal for that quadrant. Note that we can have both downscaled particle and particle- $\gamma$  coincidence for the quadrant and these need to be ORed together.

- We are in the on window or the off window. This is the equivalent of the GFLT signal sent to the DGF.

- The ADC for that quadrant is **not** busy.

- The DGF is **not** busy (indicated by the DGF SYNCH signal).

- The DAQ is **not** dead (indicated by the VME trigger module).

The ADC busy signal is provided via a special flat cable which takes the ECL signal from each ADC to a single ECL  $\rightarrow$  NIM converter. Note that the DAQ dead signal coming from the VME trigger module is also on the same cable and uses the same ECL  $\rightarrow$  NIM converter.

Note also that in 2003 we generated an artificial ADC busy which started at the same time as the real one, but lasted longer. In 2004 we used the real ADC busy signal.

The ADC gate is taken directly from the fan-in/fan-out module at the end of figure 7 and sent to the Mesytech MADC32 gate input. Then another cable goes from the gate output to the TDC corresponding to the same quadrant.

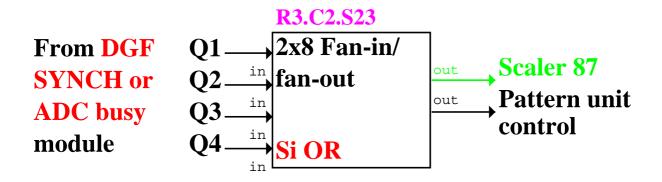

Note that the width of the output of "DGF SYNCH or ADC busy" (R3.C2.S13/15) needs to be set to about 50 ns, not for the sake of the ADC gate and TDC stop, whose signal width is determined by the gate generator, but because these signals are ORed together to make the "Si OR" signal which is used as the pattern unit's control signal. Since there is only a fan-in/fan-out between the "DGF SYNCH or ADC busy" and the pattern control, it is here where we set the width for the signal going into the pattern unit, which needs to be at least 50 ns.

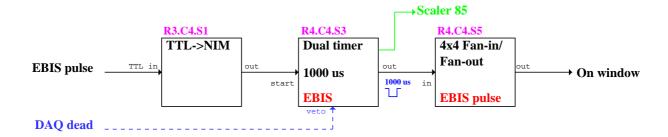

Figure 8: The generation of the EBIS window (on window). The dashed blue line corresponds to an extra connection added in 2011 to veto on windows when the DAQ is dead.

### 11 Generation of the EBIS window

Note: The "EBIS window" is the window provided by a signal from the EBIS saying there is a bunch of particles incident on the target. The terms "on window" and "off window" refer to two measuring periods of the same length, one on beam the other off beam. Consequently "EBIS window" and "on window" are synonymous terms.

A TTL signal is sent from the EBIS which after conversion to NIM is used to generate a 1 ms gate (800  $\mu$ s in previous years). The length of this gate needs to be set for the particular experiment to match the opening time of the EBIS gate.

For some reason, in 2006, we found that the dual timer was sometimes triggering on the trailing flank of the EBIS pulse as well as the leading flank, so we put it through a discriminator with a width longer than the width of the signal sent to us from the platform. Note that in this particular case, the pulse coming from the platform was 1.2 ms long, while the EBIS gate was 800  $\mu$ s long. There was no point in increasing the EBIS gate to 1.2 ms, because there were no particles during that time.

Improvements in the slow extraction in July 2011 resulted in 800  $\mu$ s being too short, so it was extended to 1 ms.

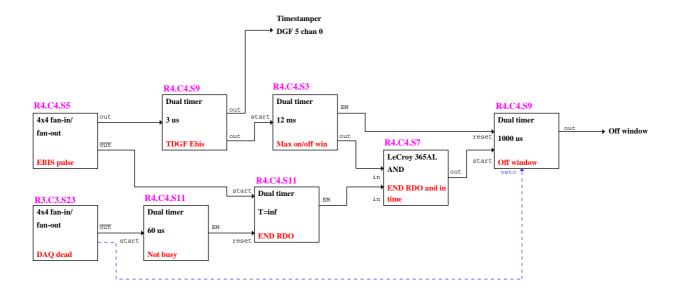

#### 12 Generation of the off window

Figure 9: The generation of the off window. The dashed blue line corresponds to an extra connection added in 2011 to veto off windows when the DAQ is dead.

We want to open one window when the EBIS gate is open (the on window) then read out the data and then open a second window (the off window) in the gap between EBIS pulses and read that data out in time to be ready for the next EBIS pulse. The on window and off window must be of equal length, so the off window length needs to be set to same as the EBIS gate.

When the EBIS signal comes, we send a 3  $\mu$ s pulse to the timestamping DGF (note that this was 5  $\mu$ s in 2003) and start a gate which is closed by the end of readout (the readout being forced at the end of the

Figure 10: The timing of the off window - the different colours correspond to two different dead times.

on window). We also start another gate, called "max on/off window", which is closed before the next EBIS pulse (12 ms in this case, but again this has been 10 ms or 12.25 ms in other experiments). This is used to truncate the off window, so we should also allow some time for reading out the off window data, in order to be ready to acquire when the next EBIS pulse comes. However, normally, it should be possible for the off window to close and readout to complete long before the next EBIS pulse.

Note that the length of the max on/off window should be checked for each experiment. It has to be long enough that there is an on window for each off window, but short enough, to make sure that the off window never gets in the way of the next EBIS pulse (only an issue at high repetition rates).

You can check this easily on the scope by triggering with "EBIS pulse" and looking at "max on/off window" and "GFLT". You should then see one GFLT pulse when the EBIS pulse comes and a second one after it, but before the end of the max on/off window. If max on/off window is too short, this second pulse is suppressed (N.B. the DAQ must be running too, since it is the readout after the off window, which triggers the on window).

In the setup, we use the fact that the end of the on window triggers readout, causing the DAQ to become dead for a while, so we wait until the DAQ is not dead again after the on window.

We start the off window 60  $\mu$ s after the end of readout (obtained from the disappearance of the DAQ dead signal) to allow the ADCs and TDCs time to start. Note that originally, it was 1  $\mu$ s but it seems that this is not enough time for everything to be ready. Since we have 12 ms in which to open the window, this extra delay isn't a problem. Until we increased this value, the DAQ would hang from time to time. Afterwards it didn't hang nearly as much.

The on window and off window should be of equal length. It is possible to have an on window without an off window, but not the other way round, since the off window is triggered by the first readout within about 12 ms after the on window. Consequently, if there is no on window, the off window also disappears. You should try to avoid this, if possible, by setting the max on/off window appropriately.

To set the two windows to the same width, the easiest thing is to look at the GFLT signal on the scope and if they are not the same length, you will see one width half the time and another the rest of the time, so the trailing edge of the pulse has two vertical lines. When it is correct, you only see a clean NIM pulse. Or you can look at the values of the scalers 1 MHz and on win and 1 MHz and of win, when using the 10 Hz clock as a fake EBIS signal. The former should be 8000 and the latter 16000 when using the 800  $\mu$ s EBIS window, but in 2011 we extended this window to 1 ms, so these numbers become 10000 and 20000.

Figure 11: The generation of the multi-off window. The differences compared to the normal off window are highlighted with red elipses

#### 12.1 Multiple off-window mode

In 2008, we did some experiments where the EBIS was triggered by the proton pulse i.e. once every 1.2 seconds at most, but with some of those pulses missing (we had 20 pulses out of 40 in the supercycle, but not equally spaced, so sometimes there was 1.2 seconds between pulses and sometimes as much as 4.8 seconds). We were interested in measuring the radioactive decay after the beam pulse, in order to determine beam composition. However, in the normal configuration of one off window for each on window, this wasn't possible.

So we used a new mode of operation, where the off window is generated not by the EBIS pulse, but by the GFLT signal. This means that an off window is generated not just 60  $\mu$ s after the end of the readout following an on window (i.e. EBIS pulse) but also following an off window. So then we get an on window followed by a series of off windows up to the limit set by max on/off window. Furthermore, we increased max on/off window from the usual 12 ms to about 1 s (keeping it short enough that it is less than the gap between proton pulses i.e. 1.2 seconds, by enough to allow plenty of time for readout).

To do this, we unplugged the signal coming from the normal output of the EBIS pulse (R4.C4.S5) going to TDGF Ebis (R4.C4.S9) and instead triggered TDGF Ebis from the GFLT output (R4.C4.S13). Then we extended max on/off win (R4.C4.S3) to 1 second.

# 13 Generation of the on/off window

The on/off window is simply the logical OR of the on window and the off window. It is used to generate the GFLT, so the terms "on/off window" and "GFLT" are synonymous.

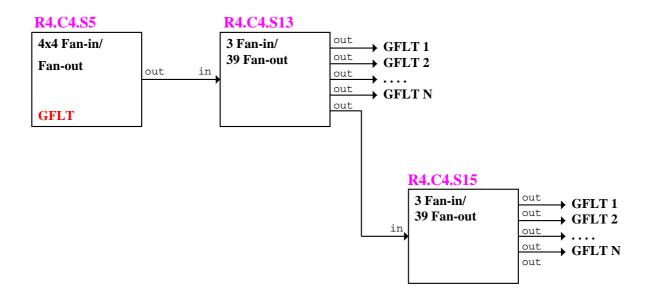

# 14 The generation of the GFLT

The global first level trigger (GFLT) signal which is sent to each DGF is the same thing as the on/off window. We use two 3 fan-in 39 fan-out modules to distribute the signal.

Typical times would be 1 ms (800  $\mu$ s in previous years) on window then about 3.2 ms readout and finally 1ms (800  $\mu$ s in previous years) off window. The on and off window lengths should be equal and fixed. The readout time varies depending on the events.

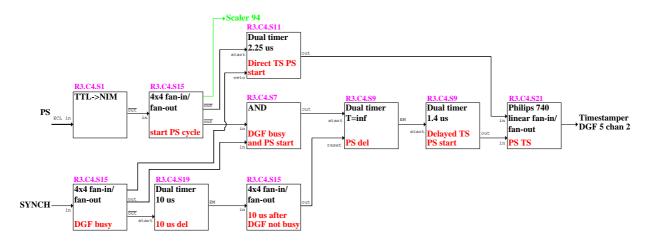

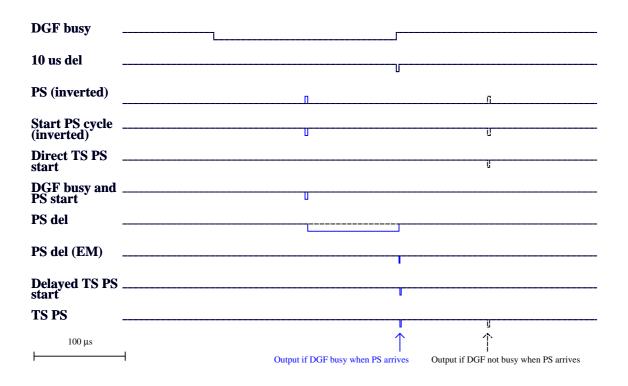

# 15 The DGF BUSY/SYNCH loop

The DGF BUSY/SYNCH loop is made using two 39-fan-in/3-fan-out modules and two 3-fan-in/39-fan-out modules. We take all the BUSY outputs from the DGFs and feed them into the fan-in inputs and then take the outputs to the fan-outs and send the result to each SYNCH input. In this way, if any one DGF is BUSY, the SYNCH line is set to logic one and if all the DGFs are acquiring it is logic zero.

# R4.C4.S5 4x4 fan-in/ fan-out out **EBIS** pulse 4x4 Fan-in/ in out on/off window Fan-out out Scaler 89 in **GFLT Dual timer** out Off window

Figure 12: The generation of the on/off window

Figure 13: The generation of the GFLT from the on/off window

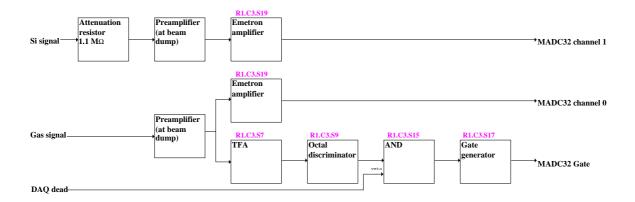

# 16 Changes for the Mesytech MADC32 modules

Like the DGFs, the Mesytech has an input which can be used to reset the clock. However, they do work in quite the same way, so they cannot be directly integrated into the BUSY-SYNCH loop.

The BUSY/CBUS output of each Mesytech module (R2.C1.S4-7) is connected to the inputs of each of the four parts of the fan-in/fan-out "ADC busy or SYNCH" module in R3.C3.S5. This is the same as for the CAEN modules, as shown on figure 7, except that while the CAEN V785 modules produce an ECL signal, which has to be converted to NIM by the converter in R3.C3.S3, the Mesytech modules generate NIM directly.

The GATE0 input takes the same gate signal as the CAEN V785 from R3.C2.S19, which is also the TDC stop.

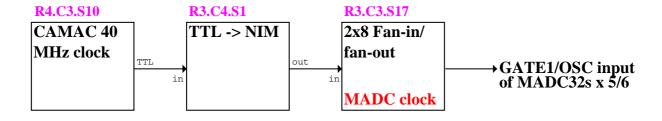

The GATE1/OSC input receives the 40 MHz clock, which is taken from a fan-in/fan-out module in R3.C3.S17. This module is in 2x8 mode, because we have five Mesytech MADC32s, which must receive this

Figure 14: The DGF BUSY/SYNCH loop

Figure 15: The generation of the 40 MHz clock signal for the MADC. One clock signal goes to each MADC-32. For Coulex there were 5 and for T-REX there were 6.

clock. The input comes from the TTL to NIM converter in R3.C4.S1 and its input comes in turn from the 40 MHz clock module in R4.C3.S10 (i.e. the module which distributes the 40 MHz clocks to the DGFs in that crate). See figure 15.

The FC/RES input is used to reset the clock of the Mesytech module. This signal comes from the second half of the 2x8 fan-in/fan-out module in R3.C3.S17. Again, as we have 5 Mesytech modules, we need five outputs from this module. The input for this module comes from the normal output of the lower part of the dual timer in R3.C4.S13. This part is used just to generate a signal of the appropriate width (set to 130 ns) and is started by the end marker of the upper part of the same module. The upper part is started by the DAQ Go signal and reset by the inverted output of the "DGF busy" signal from R3.C4.S15 with the range set to infinity. i.e. we start the dual timer when the DAQ starts and stop it when the "DGF busy" (which is the logical OR of all the busy outputs of the DGFs) becomes not busy (i.e. the moment when the DGFs

Figure 16: The MADC32 clock reset. One reset signal goes to each MADC-32. For Coulex there were 5 and for T-REX there were 6.

reset their clocks) and at that stage it generates the end marker, which is given a long enough width in the lower part of the dual timer and set to the FC/RES input of the MADC32. See figure 16.

The DAQ Go signal is taken from output 6 of the ECL to NIM converter in R3.C3.S3. This module has a flat cable input, which is split into individual twisted pair wires. The first four are for the ADC busy lines of the CAEN V785 modules, which are not used when the Mesytech modules are used. The fifth one is for DAQ dead which is connected to pins 7 and 8 of the VME trigger module (R3.C1.S2) and the sixth one is the DAQ Go, which is connected to pins 9 and 10 of the same VME trigger module.

The signal cables (flat cables) are connected in the same way as the CAEN V785 modules.

### 17 Note about special signals

We get several signals from different parts of the REX ISOLDE setup. When ISOLDE is running, we get a T1 signal when a bunch of protons hits the ISOLDE target, then a T2 signal when the gate is opened allowing beam from ISOLDE into REXTRAP. Since these two signals are correlated one-to-one with a fixed time delay between them, it is not necessary to have both. If the laser is running in on/off mode, we get a signal indicating laser on or laser off (sent into the pattern unit).

Note: The T1 and T2 signals are different for each separator (HRS and GPS). You need to hook them up in the ISOLDE control room for the appropriate separator.

The individual bunches of protons hitting the ISOLDE target form part of a supercycle and we receive the PS signal indicating the start of each supercycle. Comparing the T1 pulses to the PS signal indicates how many bunches we receive in each supercycle.

Once the ions have been trapped in the REXTRAP and ionised in the EBIS, the EBIS gate is opened to allow them into the REX accelerator. We receive the EBIS gate signal which indicates when ions are released from the EBIS and which is directly correlated to our beam. Consequently, we use this signal to generate the on-beam window.

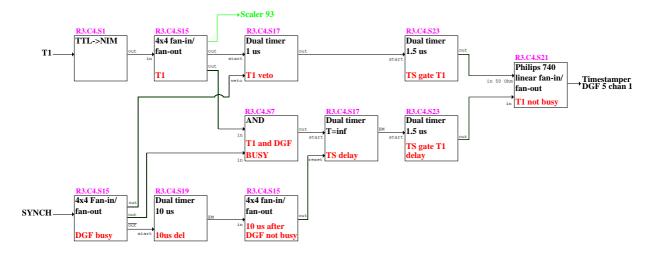

# 18 Generation of the T1 timestamp

We want two signals:

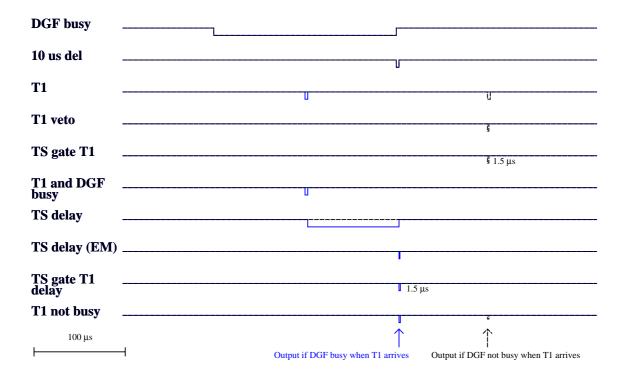

- the timestamp of the T1 signal itself, which we obtain by converting it from TTL to NIM and then generating a gate which we send via a linear fan-in/fan-out to the DGF but vetoed by the DGF busy.

- The timestamp of a time 10  $\mu$ s after the DGF starts acquiring after a T1 pulse.

In order to distinguish the two signals, they are combined using a linear fan-in/fan-out, but with one of them attenuated using a LEMO T-piece with a 50  $\Omega$  terminator.

The T1 timestamp is produced in a similar way to the proton supercycle timestamp. Both use the "10  $\mu$ s after DGF not busy" signal, so the bottom three modules in figures 19 and 17 are the same.

# 19 Generation of the proton supercycle timestamp

We want to generate a DGF timestamp giving the time of arrival of the proton supercycle start signal and a time  $10 \mu s$  after the first readout after a proton supercycle start signal.

We receive an TTL signal each time that we get a proton supercycle start which we feed into an TTL  $\rightarrow$  NIM converter. We do two things with this signal.

Figure 17: The generation of the T1 timestamp. Note that the three modules at the bottom are the same ones used for the T1 timestamp (see 19).

Figure 18: Timings for the T1 timestamp. If the DGF is not busy, when T1 comes, we generate a signal for the DGF at once, otherwise we wait until 10  $\mu$ s after it becomes not busy. In order to distinguish the two cases, we attenuate the direct one. The different colours show these two cases.

- Firstly, we use the signal to start a direct gate to indicate the start of the proton supercycle, which we send via a linear fan-in/fan-out to a timestamping DGF.

- Secondly, we want the timestamp for the first time the DGF is not busy after a supercycle start. To get this, we start a timer when the supercycle starts and the DGF is busy, and reset that timer 10  $\mu$ s after the DGF is no longer busy. Then we use the end marker of that timer to generate a gate, which is sent to the same timestamping DGF via the linear fan-in/fan-out.

Note that the bottom three modules of figures 17 and 19 are the same. i.e. they share the same  $10 \mu s$  delay.

Why don't we attenuate one of the two inputs to the linear fan-in with a 50  $\Omega$  piece in order to get different pulse heights for the two kinds of signal? We do this with the T1 signal and it seems that we should do it to PS as well. I am told this isn't really that important for PS.

Figure 19: The generation of the proton supercycle timestamp. Note that the three modules at the bottom are the same ones used for the T1 timestamp (see 17).

Figure 20: Timings for the proton supercycle timestamp. We generate a pulse for the DGF either when the PS signal comes if the DGF is not busy or 10  $\mu$ s after it becomes not busy, if it was busy when the PS signal comes. The different colours show these two cases.

I notice that in May 2005, the inverted output from the TTL to NIM converter is being used. This must have already been like that in November 2004, but I'm not sure if it was like that in July 2004. My notes from July 2004 indicate we used the normal output, but this could be an error. In any case, now we use the inverted output.

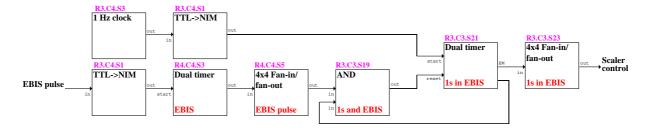

# 20 Generation of the control signals for the scalers

Normally, we want to read out the scalers every second. We convert a 1 Hz clock pulse into NIM and use it to start a gate which we fan out to the control inputs for the three scalers.

However, we only want to read when the EBIS pulse comes (on window), so we use the end marker of our gate and reset it with the EBIS pulse.